Foram encontradas 118 questões.

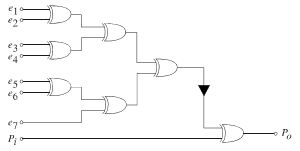

Um esquema para detecção de dados é a paridade, uma técnica utilizada para detecção de ocorrência de erros em uma transmissão digital de sinais. O circuito acima foi projetado para examinar os bits 1 de cada palavra digital transmitida e produzir bit 1 ou 0 adicional para que o total de bits 1 resulte par (paridade par) ou ímpar (paridade ímpar). O mesmo circuito pode ser usado para verificação de paridade no receptor: nesse local, caso a verificação de paridade seja falsa, significa que ocorreu um erro de transmissão. Nesse esquema específico, a palavra digital de sete bits é acoplada, bit a bit, nas entradas de e1 a e7. Os bits adicionais, disponíveis nos terminais Pi e Po, determinam a paridade da palavra digital. De acordo com essas informações e com a figura apresentada acima, julgue o próximo item.

Para que o circuito funcione como gerador de paridade, o terminal Pi deve ser ligado ao terra do circuito, para geração de paridade ímpar, ou à fonte de alimentação do circuito, para geração de paridade par.

Provas

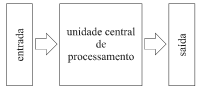

A figura acima ilustra a estrutura básica de um controlador lógico programável (CLP). A respeito dessa estrutura e do funcionamento de um CLP, julgue o item a seguir.

Na unidade central de processamento (UCP), os cartões de entrada e de saída são os elementos responsáveis pelo processamento das informações do CLP. Para essa finalidade, esses componentes fazem uso de dados que são armazenados em memórias específicas localizadas na UCP.

Provas

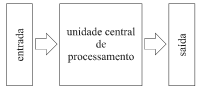

A figura acima ilustra a estrutura básica de um controlador lógico programável (CLP). A respeito dessa estrutura e do funcionamento de um CLP, julgue o item a seguir.

Os sinais de entrada e saída, como na estrutura mostrada, podem ser digitais, mas somente os de entrada podem ser analógicos.

Provas

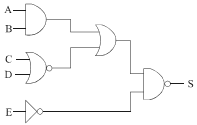

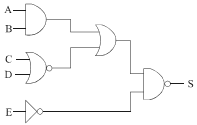

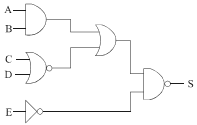

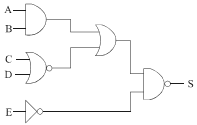

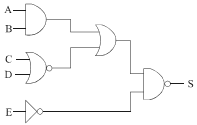

Considere que o circuito combinacional mostrado na figura acima seja implementado com portas lógicas com tecnologia TTL. Suponha que as entradas do circuito sejam representadas pelas variáveis A, B, C, D e E e que a saída do circuito seja representada pela variável S. Com relação a esse circuito, julgue o item subsequente.

O circuito utiliza uma porta lógica do tipo ou exclusivo.

Provas

Considere que o circuito combinacional mostrado na figura acima seja implementado com portas lógicas com tecnologia TTL. Suponha que as entradas do circuito sejam representadas pelas variáveis A, B, C, D e E e que a saída do circuito seja representada pela variável S. Com relação a esse circuito, julgue o item subsequente.

A expressão lógica resultando na saída S = [AB + (A+B)]E descreve corretamente a relação entre a saída e as entradas do circuito.

Provas

Considere que o circuito combinacional mostrado na figura acima seja implementado com portas lógicas com tecnologia TTL. Suponha que as entradas do circuito sejam representadas pelas variáveis A, B, C, D e E e que a saída do circuito seja representada pela variável S. Com relação a esse circuito, julgue o item subsequente.

Se as portas TTL usadas no circuito forem do tipo HS, elas terão um tempo de comutação, de um estado para outro, muito maior do que se as portas forem do tipo LS, e o consumo de potência das portas do tipo HS será menor do que o consumo das portas do tipo LS.

Provas

Considere que o circuito combinacional mostrado na figura acima seja implementado com portas lógicas com tecnologia TTL. Suponha que as entradas do circuito sejam representadas pelas variáveis A, B, C, D e E e que a saída do circuito seja representada pela variável S. Com relação a esse circuito, julgue o item subsequente.

Se a entrada E assumir o valor 1, então a saída S assumirá o valor 1, independentemente dos valores assumidos pelas variáveis A, B, C e D.

Provas

Considere que o circuito combinacional mostrado na figura acima seja implementado com portas lógicas com tecnologia TTL. Suponha que as entradas do circuito sejam representadas pelas variáveis A, B, C, D e E e que a saída do circuito seja representada pela variável S. Com relação a esse circuito, julgue o item subsequente.

Se as entradas A, B, C, D e E assumirem, respectivamente, os valores 1, 1, 0, 1 e 1, então a saída S assumirá o valor 1.

Provas

A tabela verdade acima descreve um circuito combinacional com entradas A, B e C, e saída S. Com relação a essa tabela, julgue o item que se segue.

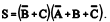

Embora não seja a expressão booleana mínima para a saída S,

a expressão booleana  expressa corretamente a saída S em função das entradas A, B

e C.

expressa corretamente a saída S em função das entradas A, B

e C.

Provas

A tabela verdade acima descreve um circuito combinacional com entradas A, B e C, e saída S. Com relação a essa tabela, julgue o item que se segue.

Na forma produto de somas, a expressão booleana mínima para

a saída S é dada por

Provas

Caderno Container