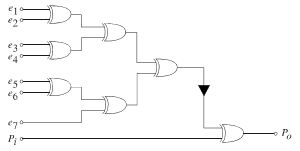

Um esquema para detecção de dados é a paridade, uma técnica utilizada para detecção de ocorrência de erros em uma transmissão digital de sinais. O circuito acima foi projetado para examinar os bits 1 de cada palavra digital transmitida e produzir bit 1 ou 0 adicional para que o total de bits 1 resulte par (paridade par) ou ímpar (paridade ímpar). O mesmo circuito pode ser usado para verificação de paridade no receptor: nesse local, caso a verificação de paridade seja falsa, significa que ocorreu um erro de transmissão. Nesse esquema específico, a palavra digital de sete bits é acoplada, bit a bit, nas entradas de e1 a e7. Os bits adicionais, disponíveis nos terminais Pi e Po, determinam a paridade da palavra digital. De acordo com essas informações e com a figura apresentada acima, julgue o próximo item.

Para uma verificação válida (verdadeira), a fim de que o circuito funcione como um verificador de paridade ímpar, o bit correspondente ao terminal Po deverá ser 0.