Foram encontradas 2.300 questões.

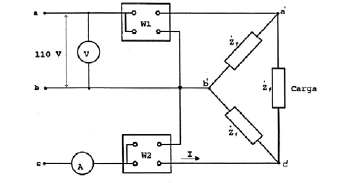

A figura acima ilustra um circuito no qual o lado de baixa tensão de um transformador trifásico é ligado em triângulo, e cuja impedância por fase é representada por uma impedância de valor finito Zf. Os enrolamentos de baixa tensão são alimentados por uma rede elétrica com tensão de linha igual a 110 V, que corresponde à tensão nominal do enrolamento. No esquema de ligação a três condutores, há um voltímetro para medição da tensão de linha e um amperímetro para medir a corrente na fase c da parte de baixa tensão. O transformador, no seu lado de alta tensão, tem tensão nominal de linha igual a 220 V, ligação em estrela e impedância por fase igual a Zg. Com base nessas informações, julgue os itens seguintes.

Considere que a conexão dos enrolamentos do lado de baixa tensão seja também em estrela, mas a impedância dos enrolamentos, por fase, continue a ser Zf. Nesse caso, como a impedância não foi modificada, a intensidade da corrente por fase ficará inalterada com relação à intensidade de corrente que seria verificada para a carga em triângulo.

Provas

A respeito do controle de execução, documentação e fiscalização de obras e serviços, julgue os itens seguintes.

O diário de obras é considerado ponto de referência para as medições de obras.

Provas

Julgue os itens subsequentes, relativos a máquinas elétricas.

Em um motor de corrente contínua, invertendo-se simultaneamente corrente do enrolamento de campo e a corrente de armadura, ocorrerá a inversão do sentido de rotação da máquina.

Provas

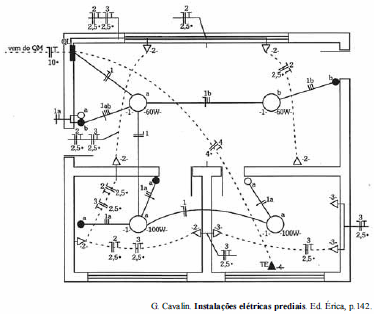

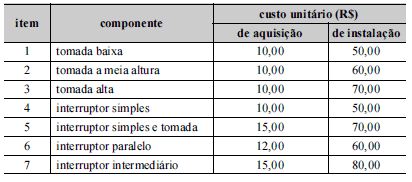

A figura acima mostra a planta baixa de parte de uma residência. No projeto dessa residência, adotam-se a simbologia e a nomenclatura padrão de projetos de instalações residenciais. A tabela a seguir, que apresenta custos de determinados componentes, serve como base para quantitativo de material, elaboração de orçamento e custos da instalação desse projeto.

Com base nessas informações, julgue os itens subsequentes, considerando as normas pertinentes para instalações elétricas prediais de baixa tensão.

Os circuitos 1 e 2 possuem os condutores fase, neutro e terra.

Provas

Considere que um sinal senoidal analógico de frequência 40 MHz seja transmitido por meio de um cabo coaxial a um conversor analógico/digital (A/D), que realiza conversão com resoluções de 8 bits e taxa de amostragem fS, e que se pretenda converter esse sinal analógico em um sinal digital quantizado em 80 níveis diferentes, no mínimo. Com base nessas informações e considerando, ainda, que log1080 = 1,903 e log102 = 0,3010, julgue os próximos itens.

É conveniente a utilização de um cabo coaxial de comprimento próximo a 1,9 m para minimização de perdas por irradiação.

Provas

Considere que um sinal senoidal analógico de frequência 40 MHz seja transmitido por meio de um cabo coaxial a um conversor analógico/digital (A/D), que realiza conversão com resoluções de 8 bits e taxa de amostragem fS, e que se pretenda converter esse sinal analógico em um sinal digital quantizado em 80 níveis diferentes, no mínimo. Com base nessas informações e considerando, ainda, que log1080 = 1,903 e log102 = 0,3010, julgue os próximos itens.

A taxa de amostragem mínima teórica (fSmin) do conversor A/D deve ser de 80 milhões de amostras por segundo.

Provas

Considere que um sinal senoidal analógico de frequência 40 MHz seja transmitido por meio de um cabo coaxial a um conversor analógico/digital (A/D), que realiza conversão com resoluções de 8 bits e taxa de amostragem fS, e que se pretenda converter esse sinal analógico em um sinal digital quantizado em 80 níveis diferentes, no mínimo. Com base nessas informações e considerando, ainda, que log1080 = 1,903 e log102 = 0,3010, julgue os próximos itens.

A eficiência de codificação do conversor A/D é superior a 85%.

Provas

O circuito acima representa uma porta lógica digital implementada com a tecnologia NMOS. Os transistores de chaveamento (com entradas vA e vB) são idênticos e do tipo enriquecimento, mas o transistor de carga é do tipo depleção. As tensões de limiar dos transistores de chaveamento e carga são 1 V e -3 V, respectivamente. Para esse circuito, o nível lógico alto (1 digital) é definido como qualquer tensão analógica compreendida entre 3,5 V e 5 V, e o nível lógico baixo (0 digital) corresponde às tensões analógicas entre 0 e 1,8 V. Esse circuito apresenta duas peculiaridades:

I se pelo menos um dos transistores de chaveamento operar com entrada em 5 V, a tensão de saída vO não excederá 0,3 V;

II somente com ambas as entradas simultaneamente no nível lógico baixo, a saída atinge o nível lógico alto.

Com base nessas informações, julgue os itens subsequentes.

Em condições estáticas, isto é, sem chaveamento dos níveis de entrada, a máxima dissipação de potência ocorre quando ambas as entradas estiverem fixadas em 5 V.

Provas

O circuito acima representa uma porta lógica digital implementada com a tecnologia NMOS. Os transistores de chaveamento (com entradas vA e vB) são idênticos e do tipo enriquecimento, mas o transistor de carga é do tipo depleção. As tensões de limiar dos transistores de chaveamento e carga são 1 V e -3 V, respectivamente. Para esse circuito, o nível lógico alto (1 digital) é definido como qualquer tensão analógica compreendida entre 3,5 V e 5 V, e o nível lógico baixo (0 digital) corresponde às tensões analógicas entre 0 e 1,8 V. Esse circuito apresenta duas peculiaridades:

I se pelo menos um dos transistores de chaveamento operar com entrada em 5 V, a tensão de saída vO não excederá 0,3 V;

II somente com ambas as entradas simultaneamente no nível lógico baixo, a saída atinge o nível lógico alto.

Com base nessas informações, julgue os itens subsequentes.

O circuito desempenha a função de porta NAND (complemento da porta lógica E) de duas entradas.

Provas

O circuito acima representa uma porta lógica digital implementada com a tecnologia NMOS. Os transistores de chaveamento (com entradas vA e vB) são idênticos e do tipo enriquecimento, mas o transistor de carga é do tipo depleção. As tensões de limiar dos transistores de chaveamento e carga são 1 V e -3 V, respectivamente. Para esse circuito, o nível lógico alto (1 digital) é definido como qualquer tensão analógica compreendida entre 3,5 V e 5 V, e o nível lógico baixo (0 digital) corresponde às tensões analógicas entre 0 e 1,8 V. Esse circuito apresenta duas peculiaridades:

I se pelo menos um dos transistores de chaveamento operar com entrada em 5 V, a tensão de saída vO não excederá 0,3 V;

II somente com ambas as entradas simultaneamente no nível lógico baixo, a saída atinge o nível lógico alto.

Com base nessas informações, julgue os itens subsequentes.

Enquanto ambas as entradas vA e vB estiverem fixadas no nível lógico baixo, é possível que haja dissipação apreciável de potência pelo circuito.

Provas

Caderno Container