Foram encontradas 60 questões.

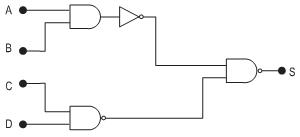

O circuito digital acima representa um circuito composto por três portas lógicas com quatro entradas A, B, C e D e uma saída S.

Qual é a expressão booleana da saída S?

Provas

Questão presente nas seguintes provas

Os amplificadores operacionais apresentam importantes características, dentre as quais se destaca a seguinte:

Provas

Questão presente nas seguintes provas

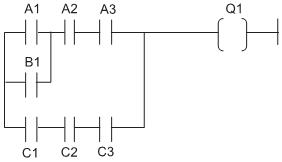

O diagrama abaixo é um Ladder representando uma linguagem de programação gráfica, que trata da lógica de contatos, e é muito usada na programação de CLP.

Qual é o circuito lógico que representa a função booleana, equivalente ao Diagrama Ladder mostrado acima?

Qual é o circuito lógico que representa a função booleana, equivalente ao Diagrama Ladder mostrado acima?

Provas

Questão presente nas seguintes provas

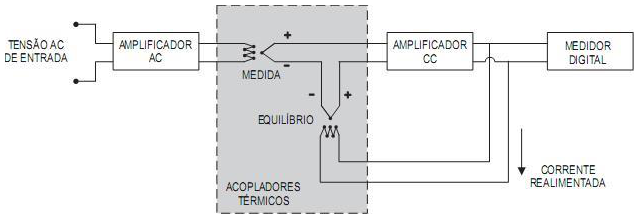

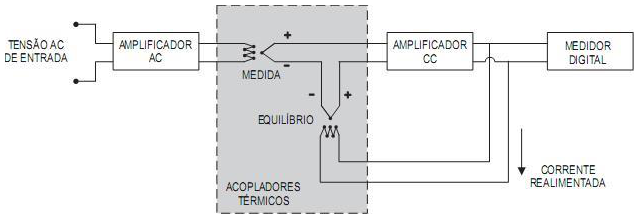

O circuito abaixo mostra um voltímetro TRUE-RMS, no qual a medida e o equilíbrio dos acopladores térmicos são realizados no mesmo ambiente térmico.

Analisando-se o circuito, verifica-se que

Analisando-se o circuito, verifica-se que

Provas

Questão presente nas seguintes provas

A ABNT (IEC 61511), que trata dos Sistemas Integrados de Segurança (SIS), apresenta dois tipos de requisitos: os funcionais e os de integridade, com o objetivo de prevenir a ocorrência de falhas aleatórias e sistemáticas. Para tanto, os dois principais conceitos são o Nível de Integridade de Segurança (Safety Integrity Level – SIL) e o Ciclo de Vida de Segurança (Safety Lifecycle – SLC).

A principal diferença entre esses dois conceitos encontra-se em:

A principal diferença entre esses dois conceitos encontra-se em:

Provas

Questão presente nas seguintes provas

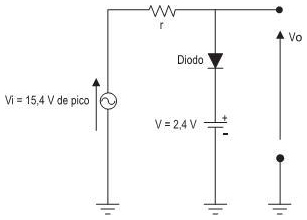

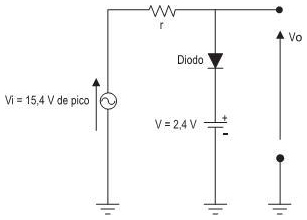

Admita-se que todos os componentes do circuito abaixo sejam ideais, que V = 2,4 volts, que r seja calculado adequadamente, obedecendo-se às limitações do diodo e, ainda, que o circuito seja alimentado por uma tensão senoidal de entrada Vi = 15,4 volts de pico com frequência compatível com as características do diodo.

Quais são, respectivamente, o valor mínimo da tensão de entrada “Vi”, em volts, para a qual o diodo conduz, e o valor da tensão “Vo”, em volts, nessas mesmas condições?

Quais são, respectivamente, o valor mínimo da tensão de entrada “Vi”, em volts, para a qual o diodo conduz, e o valor da tensão “Vo”, em volts, nessas mesmas condições?

Provas

Questão presente nas seguintes provas

No controle de processos industriais em malha aberta, um sinal de controle aguarda que, ao final de certo tempo, a variável controlada chegue a um determinado valor. O sistema opera sem que nenhuma ação de controle seja realizada, isto é, as informações sobre a evolução do processo não são usadas para determinar o sinal de controle a ser aplicado em um dado instante. Por outro lado, no controle em malha fechada, usa-se realimentação da saída para entrada. Para torná-lo mais preciso, o sinal de saída é comparado a uma referência (set point), e o erro entre esses dois sinais é usado para compor o sinal de controle que será aplicado ao processo, corrigindo o erro entre a saída e a referência.

Nesse sentido, observa-se que

Nesse sentido, observa-se que

Provas

Questão presente nas seguintes provas

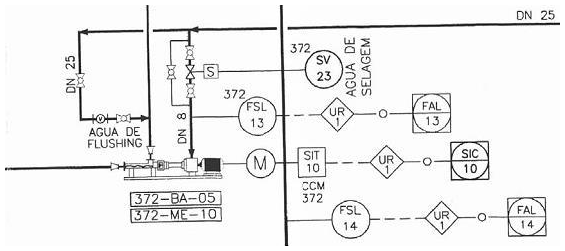

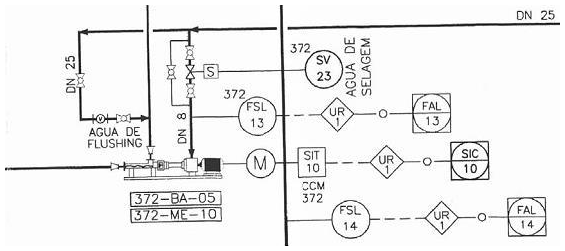

A Figura mostrada abaixo é parte de um desenho.

Esse desenho é correspondente a um documento básico de projeto de instrumentação denominado

Esse desenho é correspondente a um documento básico de projeto de instrumentação denominado

Provas

Questão presente nas seguintes provas

Um técnico necessita fazer a calibração de um voltímetro digital e, para isso, planeja usar o esquema a seguir.

O equipamento 1 é uma fonte de tensão, padrão ajustável, cujo valor da tensão é medido pelo equipamento 2, um voltímetro de referência com grau de incerteza de medição desprezível. O equipamento 3 é o voltímetro digital a ser calibrado.

Nesse contexto, verifica-se que

O equipamento 1 é uma fonte de tensão, padrão ajustável, cujo valor da tensão é medido pelo equipamento 2, um voltímetro de referência com grau de incerteza de medição desprezível. O equipamento 3 é o voltímetro digital a ser calibrado.

Nesse contexto, verifica-se que

Provas

Questão presente nas seguintes provas

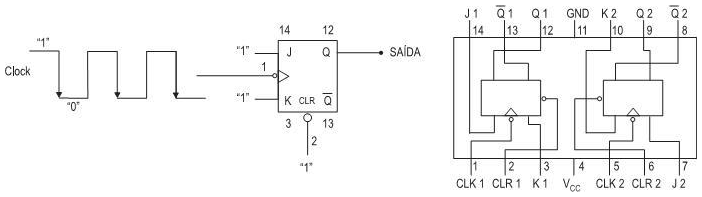

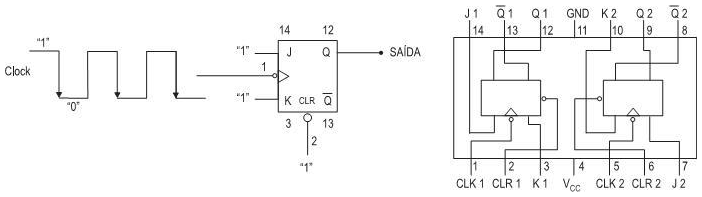

Usando-se um circuito integrado (CI) da família TTL, contendo dois J-K flip-flop, mestre-escravos independentes e CLEAR assíncrono, montou-se um circuito. Para tal, usou-se apenas um desses flip-flop, cujos pinos estão representados no circuito, de acordo com o diagrama de conexão do CI, obtido do fabricante, ambos apresentados a seguir.

Sabe-se que o CLEAR está em “0”, que o flip-flop apresenta saídas Q = “0” e Q = “1”, que a transição ocorre na descida do clock (conforme pode ser visto na mesma Figura) e que a frequência é compatível com as características do CI. (A fonte de alimentação e o terra foram omitidos, propositadamente, para não sobrecarregar o desenho.)

Se “1”, um lógico, representa nível alto, e “0”, zero lógico, representa nível baixo, qual é a frequência do sinal na saída, tomado em Q, com relação à frequência do clock?

Sabe-se que o CLEAR está em “0”, que o flip-flop apresenta saídas Q = “0” e Q = “1”, que a transição ocorre na descida do clock (conforme pode ser visto na mesma Figura) e que a frequência é compatível com as características do CI. (A fonte de alimentação e o terra foram omitidos, propositadamente, para não sobrecarregar o desenho.)

Se “1”, um lógico, representa nível alto, e “0”, zero lógico, representa nível baixo, qual é a frequência do sinal na saída, tomado em Q, com relação à frequência do clock?

Provas

Questão presente nas seguintes provas

Cadernos

Caderno Container