Foram encontradas 130 questões.

|

entrada a |

entrada b | entrada c |

saída f |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | X |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

Considerando a tabela-verdade acima, que descreve o comportamento de um circuito convencional com três entradas e uma saída, e na qual X representa dont’care (não importa), julgue o item seguinte.

A função de saída f será sempre dependente da entrada B, mesmo na implementação com mínimo número de portas lógicas.

Provas

|

entrada a |

entrada b | entrada c |

saída f |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | X |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

Considerando a tabela-verdade acima, que descreve o comportamento de um circuito convencional com três entradas e uma saída, e na qual X representa dont’care (não importa), julgue o item seguinte.

O don’t care deve ser necessariamente considerado como tendo nível 1.

Provas

|

entrada a |

entrada b | entrada c |

saída f |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | X |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

Considerando a tabela-verdade acima, que descreve o comportamento de um circuito convencional com três entradas e uma saída, e na qual X representa dont’care (não importa), julgue o item seguinte.

A função de saída f pode não necessitar de um circuito de implementação, por poder ser exatamente igual a uma das entradas.

Provas

|

entrada a |

entrada b | entrada c |

saída f |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | X |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

Considerando a tabela-verdade acima, que descreve o comportamento de um circuito convencional com três entradas e uma saída, e na qual X representa dont’care (não importa), julgue o item seguinte.

Essa tabela só pode ser implementada por meio de um circuito digital sequencial

Provas

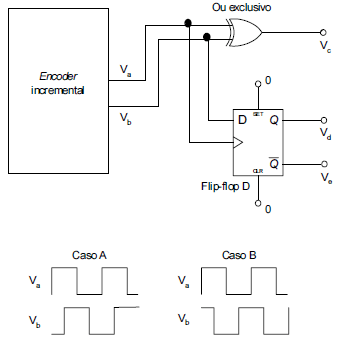

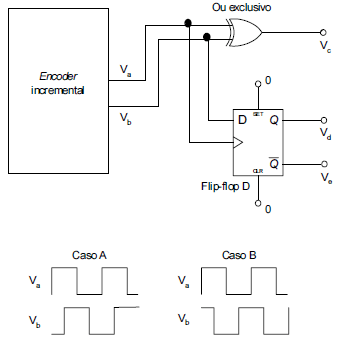

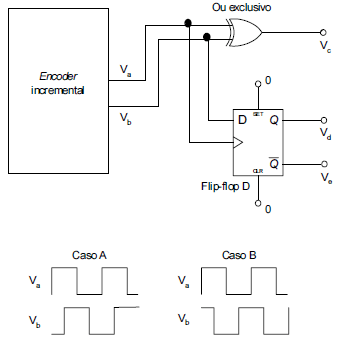

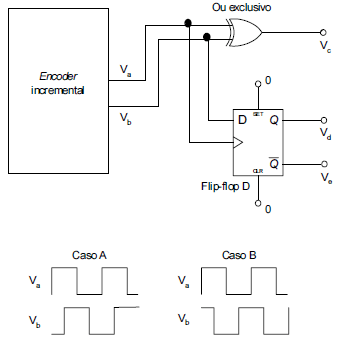

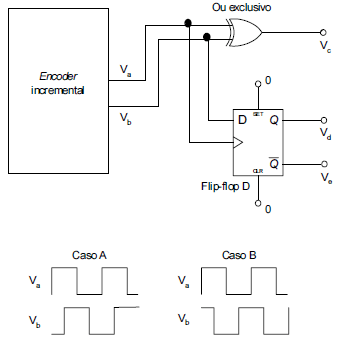

Um encoder incremental possui dois sinais de saída, na forma de onda quadrada, de mesma frequência e defasados em ¼ de ciclo. Assumindo que as saídas dos canais tenham ciclo de trabalho de 50%, existem duas possibilidades para a temporização dos mesmos, conforme indicado por caso A e caso B na figura acima. Os sinais do encoder incremental são processados pelo circuito digital indicado na mesma figura. Acerca do funcionamento desse circuito em regime permanente, e considerando que todos os componentes do circuito são ideais, julgue o item subsequente.

Se as saídas do encoder incremental se comportarem como ilustrado no caso B, então a saída Ve do Flip-flop do tipo D sempre estará em nível lógico baixo.

Provas

Um encoder incremental possui dois sinais de saída, na forma de onda quadrada, de mesma frequência e defasados em ¼ de ciclo. Assumindo que as saídas dos canais tenham ciclo de trabalho de 50%, existem duas possibilidades para a temporização dos mesmos, conforme indicado por caso A e caso B na figura acima. Os sinais do encoder incremental são processados pelo circuito digital indicado na mesma figura. Acerca do funcionamento desse circuito em regime permanente, e considerando que todos os componentes do circuito são ideais, julgue o item subsequente.

Como a entrada CLR do flip-flop do tipo D é ativada por nível alto, e essa entrada está em nível baixo, então a saída Ve sempre estará em nível alto.

Provas

Um encoder incremental possui dois sinais de saída, na forma de onda quadrada, de mesma frequência e defasados em ¼ de ciclo. Assumindo que as saídas dos canais tenham ciclo de trabalho de 50%, existem duas possibilidades para a temporização dos mesmos, conforme indicado por caso A e caso B na figura acima. Os sinais do encoder incremental são processados pelo circuito digital indicado na mesma figura. Acerca do funcionamento desse circuito em regime permanente, e considerando que todos os componentes do circuito são ideais, julgue o item subsequente.

Se as saídas do encoder incremental se comportarem conforme ilustrado no caso A, então a saída Vd do flip-flop do tipo D sempre estará em nível lógico alto.

Provas

Um encoder incremental possui dois sinais de saída, na forma de onda quadrada, de mesma frequência e defasados em ¼ de ciclo. Assumindo que as saídas dos canais tenham ciclo de trabalho de 50%, existem duas possibilidades para a temporização dos mesmos, conforme indicado por caso A e caso B na figura acima. Os sinais do encoder incremental são processados pelo circuito digital indicado na mesma figura. Acerca do funcionamento desse circuito em regime permanente, e considerando que todos os componentes do circuito são ideais, julgue o item subsequente.

Se o sinal Vb estivesse sempre em nível alto, a porta ou-exclusivo (exclusive-Or) inverteria o sinal Va.

Provas

Um encoder incremental possui dois sinais de saída, na forma de onda quadrada, de mesma frequência e defasados em ¼ de ciclo. Assumindo que as saídas dos canais tenham ciclo de trabalho de 50%, existem duas possibilidades para a temporização dos mesmos, conforme indicado por caso A e caso B na figura acima. Os sinais do encoder incremental são processados pelo circuito digital indicado na mesma figura. Acerca do funcionamento desse circuito em regime permanente, e considerando que todos os componentes do circuito são ideais, julgue o item subsequente.

O sinal Vc possui frequência duas vezes maior que a frequência do sinal Vb.

Provas

É normal em satélites modernos a utilização de transponders. A respeito desse assunto, julgue o item abaixo.

Cada transponder consiste de um diplexer, o qual realiza simultaneamente as funções de receptor e transmissor.

Provas

Caderno Container