Foram encontradas 20.584 questões.

Provas

Disciplina: Engenharia Eletrônica

Banca: IESES

Orgão: Polícia Científica-SC

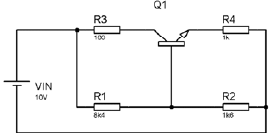

II. Esse circuito possui uma configuração do transistor como fonte de corrente.

III. A tensão sobre o Resistor R4 é 0,90V

IV. O funcionamento desse circuito independe dos dados de fabricação do transistor Q1.

Provas

Disciplina: Engenharia Eletrônica

Banca: IESES

Orgão: Polícia Científica-SC

Provas

Disciplina: Engenharia Eletrônica

Banca: IESES

Orgão: Polícia Científica-SC

Provas

Disciplina: Engenharia Eletrônica

Banca: IESES

Orgão: Polícia Científica-SC

Provas

Disciplina: Engenharia Eletrônica

Banca: IESES

Orgão: Polícia Científica-SC

Provas

Provas

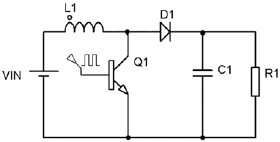

Com relação aos conversores estáticos de potência, marque ( V ) para as afirmativas verdadeiras e ( F ), para as

( ) A topologia buck abaixador têm sua tensão de saída inversamente proporcional ao tempo que a chave permanece desligada.

( ) O conversor tipo boost elevador têm seu ganho estático fortemente influenciado pela carga quando operado no modo de condução descontínua.

( ) Tempo morto é um termo utilizado para designar o intervalo de tempo entre comutações com o objetivo de se evitar curto circuito.

( ) O conversor buck boost abaixador elevador possuí dois estágios de operação no modo de condução contínua: armazenamento de energia no capacitor acumulador e transferência de energia para o indutor de saída.

( ) A relação entre o tempo que a chave de potência permanece fechada e o período de comutação é conhecida como razão cíclica.

Assinale a alternativa que contém a sequência CORRETA de associação, de cima para baixo.

Provas

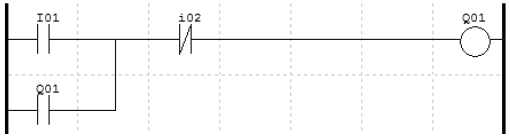

Considere o programa em diagrama de contatos apresentado na figura abaixo implementado em um CLP. Em t = 0, todas as variáveis encontram se em nível lógico 0. Os gráficos apresentam as variações dos sinais I01 e I02 a partir de t > 0. Os níveis lógicos do sinal Q01 para os tempos A, B, C e D serão, respectivamente.

Provas

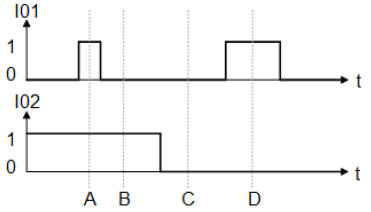

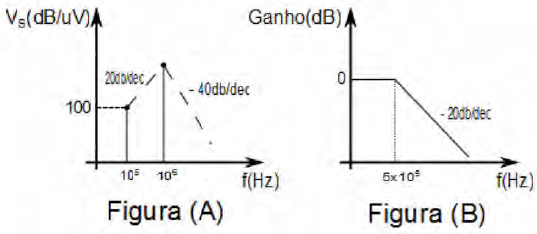

Um sinal periódico "Vs", que é resultado da captação de um sinal através de um sensor, tem sua representação no domínio da frequência mostrada na figura (A). Um filtro, cujo diagrama de bode de ganho é apresentado na figura (B), é utilizado para condicionar o referido sinal para ser ainda amplificado e convertido através de um conversor analógico/digital. Considerando esta situação, marque (V) para as afirmações verdadeiras e (F) para as afirmações falsas.

( ) O diagrama de bode apresentado é de um filtro de segunda ordem. f(Hz)

( ) A amplitude do sinal na saída do filtro para as frequências de 105 Hz, 107 Hz e 109 Hz é respectivamente de 100 dB/uV, 74 dB/uV e - 66 dB/uV.

( ) Para o cálculo da amplitude de um sinal em dB/uV utiliza-se 20.log10(Vs/ 1x10-6).

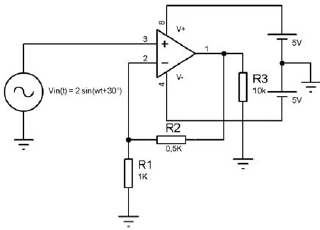

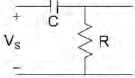

( ) O diagrama de bode, apresentado na Figura (B), é implementado com o seguinte circuito

( ) O diagrama de bode, apresentado na Figura (B), é implementado com o seguinte circuito

Marque a opção que contenha a sequência CORRETA, de cima para baixo:

Provas

Caderno Container